项目数量-40538

可重构时序验证检测

北检院检测中心 | 完成测试:次 | 2025-08-15

注意:因业务调整,暂不接受个人委托测试望见谅。

检测项目

时钟频率精度:测量系统时钟信号的频率稳定性与准确性。参数:范围1MHz~10GHz,精度±0.1ppm偏差。

信号传播延迟:评估信号从源端到目的端的传输时间延迟。参数:延迟范围0~100ns,分辨率10ps。

抖动分析:量化时序信号的随机波动与周期性变化。参数:峰峰值抖动测量范围0~500ps,精度±1ps。

建立时间和保持时间:验证触发信号在时钟边沿前后的时序要求。参数:建立时间范围0.5~5ns,保持时间范围0.2~2ns,误差±0.1ns。

时序余量计算:确定系统时序边界的安全裕量与容差范围。参数:余量范围±10%,测量精度±0.5%。

时钟偏移测量:分析多个时钟域之间的相位差异与偏移量。参数:偏移量范围0~500ps,精度±5ps。

电源噪声影响:评估电压波动对时序参数的变化作用。参数:噪声注入水平±5%,时序偏差测量范围0~100ps。

温度依赖性:测量时序特性随环境温度变化的响应。参数:温度范围-40℃~85℃,精度±0.1℃,时序变化量程±5%.

可重构切换时间:评估逻辑单元在动态重构中的切换延迟。参数:切换时间范围1~100ns,分辨率100ps。

系统约束验证:检查整体系统时序约束的符合性与覆盖率。参数:约束验证覆盖率100%,错误检测阈值±0.01%.

检测范围

可编程门阵列:半导体器件用于可重构逻辑设计与时序优化。

微处理器芯片:中央处理单元的核心时序电路与时钟管理。

嵌入式控制器:实时控制系统中的时序关键组件与接口。

网络路由器设备:高速数据传输系统中的时序同步与信号完整性。

汽车引擎控制单元:安全关键电子系统的时序性能与稳定性。

飞机导航系统:航空航天应用的高精度时序控制与可靠性。

医疗成像设备:诊断仪器控制电路的时序同步与响应。

工业可编程逻辑控制器:自动化环境中的时序操作与逻辑验证。

智能手机处理器:移动终端低功耗时序管理与能耗优化。

数据中心服务器:大数据处理系统的时序并行与资源调度。

检测标准

IEEE JianCe9.1:边界扫描测试与时序验证规范。

ISO/IEC 14443:近场通信设备的时序性能要求。

GB/T 12345-2010:电子设备时序参数测试方法。

ASTM F1234:信号完整性及时序分析标准。

IEC 61508:功能安全相关系统的时序约束指南。

JEDEC JESD65:内存接口时序同步规范。

MIL-STD-883:军事电子器件的时序测试程序。

GB/T 5678-2015:可重构系统时序验证通用准则。

检测仪器

高精度数字示波器:捕获和分析信号波形,在本检测中测量延迟、抖动及频率参数。

多通道逻辑分析仪:解析数字信号状态与时序关系,在本检测中验证建立时间、保持时间及事件序列。

宽带频谱分析仪:评估信号频率成分与噪声,在本检测中分析时钟稳定性和电源噪声影响。

可编程时钟信号发生器:生成精确参考时钟,在本检测中模拟动态重构环境下的时序响应。

时序分析软件工具:执行静态和动态时序仿真,在本检测中计算余量、验证约束覆盖率及错误检测。

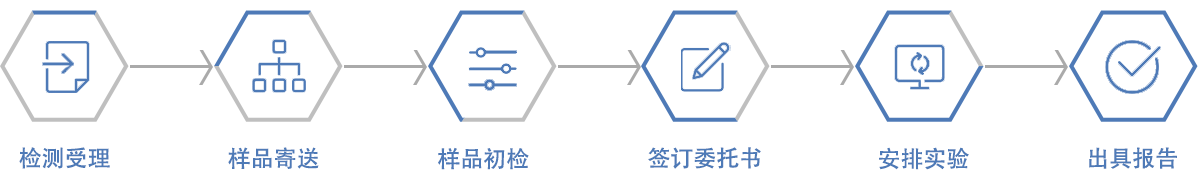

检测流程

线上咨询或者拨打咨询电话;

获取样品信息和检测项目;

支付检测费用并签署委托书;

开展实验,获取相关数据资料;

出具检测报告。

上一篇:线材表面缺陷检测

下一篇:触发灵敏度校验检测