项目数量-0

时钟域交叉验证检测

北检院检测中心 | 完成测试:次 | 2025-08-15

注意:因业务调整,暂不接受个人委托测试望见谅。

检测项目

亚稳态检测:评估信号在异步时钟转换时的稳定性风险;具体检测参数包括亚稳态概率统计、最小解决时间测量、亚稳态窗口宽度分析。

建立时间检查:验证数据信号在时钟上升沿前的稳定时间;具体检测参数包括最小建立时间要求、建立时间裕量计算、建立时间违反点识别。

保持时间检查:确认数据信号在时钟上升沿后的保持时间;具体检测参数包括最小保持时间要求、保持时间裕量计算、保持时间违反点分析。

时钟偏斜分析:测量不同时钟域时钟信号到达延迟差异;具体检测参数包括最大时钟偏斜值、偏斜分布统计、偏斜对时序影响评估。

数据路径验证:检查跨时钟域数据传输路径的完整性;具体检测参数包括数据位错误率、路径延迟一致性、信号失真幅度测量。

握手协议检测:评估异步握手机制同步性;具体检测参数包括握手信号响应时间、协议冲突发生率、请求/确认信号抖动分析。

同步器有效性测试:验证同步器电路对亚稳态缓解效果;具体检测参数包括同步器级数评估、亚稳态消除率、同步器延迟测量。

复位信号稳定性检查:分析复位信号在不同时钟域同步可靠性;具体检测参数包括复位解除时间、复位信号毛刺检测、复位时序一致性验证。

时钟门控机制测试:评估时钟门控在跨域应用的时序影响;具体检测参数包括门控使能延迟、门控关闭抖动、时钟门控失效概率。

故障安全性机制验证:确认安全机制在时钟域交叉中的可靠性;具体检测参数包括故障注入响应时间、安全状态切换延迟、错误覆盖率计算。

检测范围

ASIC芯片设计:集成电路中不同时钟域逻辑模块间的信号交互验证。

FPGA实现:可编程逻辑器件内异步时钟区域数据传输可靠性测试。

微处理器核心:CPU内部多时钟域调度单元间时序协调性检测。

通信接口模块:如以太网或USB控制器中收发数据的跨时钟边界同步分析。

存储器接口电路:DRAM或SRAM控制器与存储单元时钟域交叉时序检查。

高速串行总线系统:PCIe或SATA接口时钟域转换信号完整性评估。

汽车电子控制单元:车载ECU内传感器与处理器异步时钟数据交换验证。

工业自动化控制器:PLC系统多时钟域实时数据传输稳定性测试。

消费电子设备:智能手机或平板电脑中显示屏与处理器时钟域交互检测。

航空航天电子系统:飞行控制计算机内冗余时钟域故障安全机制验证。

检测标准

ISO 26262-2018功能安全标准:规范汽车电子时钟域交叉故障风险分析要求。

IEC 61508-2010安全完整性等级标准:定义工业系统时钟域可靠性验证框架。

IEEE Std JianCe9.1边界扫描测试标准:指导跨时钟域信号完整性测试方法。

GB/T 20234-2019数字集成电路测试标准:规定时钟域交叉时序参数测量准则。

ASTM F2592-2008电子系统可靠性评估标准:涵盖异步时钟接口失效模式分析。

ISO/IEC 15408信息技术安全评估标准:包含时钟域数据保护机制验证条款。

GB/T 33781-2017高速电路设计规范:明确时钟偏斜和建立/保持时间检测流程。

IEEE 802.3以太网标准:定义网络设备时钟域交叉数据传输测试要求。

IEC 62132集成电路电磁兼容标准:涉及时钟信号干扰对跨域传输影响检测。

GB/T 17626电子兼容性测试标准:规范时钟抖动对域交叉稳定性验证方法。

检测仪器

逻辑分析仪:捕获和显示数字信号波形;具体功能包括监视时钟域交叉点信号时序、测量建立/保持时间违反情况。

数字存储示波器:记录高速信号瞬态响应;具体功能包括分析时钟偏斜、检测亚稳态事件持续时间。

时序分析软件工具:模拟和验证电路时序路径;具体功能包括计算时钟域裕量、识别跨域数据传输错误点。

信号发生器:模拟时钟和数据信号;具体功能包括注入异步时钟测试模式、评估握手协议响应时间。

边界扫描测试仪:执行基于标准的互连测试;具体功能包括验证时钟域边界信号完整性、检测路径延迟异常。

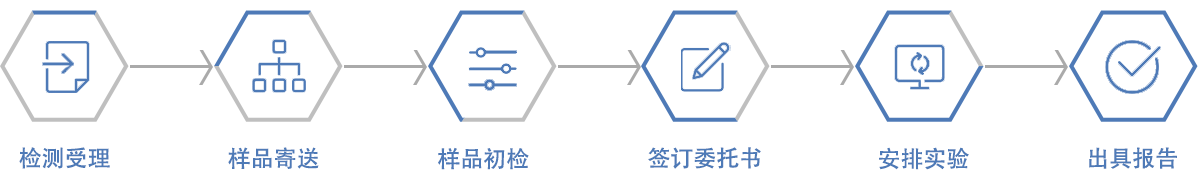

检测流程

线上咨询或者拨打咨询电话;

获取样品信息和检测项目;

支付检测费用并签署委托书;

开展实验,获取相关数据资料;

出具检测报告。

上一篇:多周期路径试验检测

下一篇:时间借用窗口监测检测