项目数量-0

芯片推拉力性能检测

北检院检测中心 | 完成测试:次 | 2025-05-12

注意:因业务调整,暂不接受个人委托测试望见谅。

检测项目

芯片推拉力性能检测包含三大核心测试模块:

焊球推力测试:评估BGA/CSP封装中焊球与基板间的结合强度,重点监测最大推力值及断裂模式

焊线拉力测试:测量金线/铜线与芯片焊盘、引线框架间的键合强度,识别颈部断裂或界面剥离等失效类型

芯片剪切力测试:测定裸片与基板粘接层的抗剪切能力,验证环氧树脂或DAF膜的粘接可靠性

界面分层测试:通过特定角度推刀实施分层强度检测,评估塑封料与芯片/基板间的界面结合质量

检测范围

| 封装类型 | 测试对象 | 适用标准 |

|---|---|---|

| BGA/LGA封装 | 锡球阵列、基板焊盘 | JESD22-B117A |

| QFN/DFN封装 | 外露焊盘、铜柱结构 | MIL-STD-883H |

| CSP/WLP封装 | 微凸点、RDL层 | IPC-9701A |

| 功率器件封装 | 铜夹片、烧结银层 | AEC-Q006 Rev.A |

检测方法

标准化测试流程包含以下关键步骤:

样品制备:采用精密切割设备获取截面样本,使用离子研磨仪处理检测界面至纳米级粗糙度

参数设定:依据JEDEC JESD22-B109规范设定测试速度(典型值50-500μm/s)、作用角度(0°或45°)及环境温度(-65℃至150℃)

接触定位:通过激光定位系统实现±1μm精度的探针定位,采用闭环伺服控制确保施力方向精确性

数据采集:以10kHz采样率记录载荷-位移曲线,同步获取最大破坏力值及弹性变形阶段特征参数

失效分析:结合SEM/EDS对断裂面进行形貌观察和元素分析,判定失效模式(内聚断裂/界面断裂)

检测仪器

多功能推拉力测试系统(Dage Series 4000)

- 量程范围:0.01N-500N

- 分辨率:0.001N

- 集成热台模块支持-55℃至300℃温控测试

- 配备6轴光学对位系统及激光位移传感器

微力值精密测试仪(XYZTEC Condor)

- 超低量程模式:0.001N-10N

- Z向重复定位精度±0.15μm

- 支持纳米级位移控制模式

- 集成真空吸附夹具系统

高温剪切力测试装置(Nordson DAGE TCT系列)

- 最高工作温度400℃

- 剪切速度0.001-20mm/s可调

- 配备氮气环境腔体

- 兼容150mm晶圆级测试需求

三维形貌分析系统(Bruker ContourX)

- 白光干涉垂直分辨率0.1nm

- 100X物镜视场0.07×0.05mm

- 三维表面粗糙度分析功能

- 断裂面三维重构能力达亚微米级精度

| 封装类型 | 最小接受标准(N) | ||

|---|---|---|---|

| 焊球直径≤200μm | 焊球直径>200μm | 铜柱结构 | |

| CSP封装(0.4mm间距) | 0.30±0.05 | - | - |

| FCBGA(1.0mm间距) | - | 1.25±0.15 | - |

| 3D IC TSV结构(50μm直径) | |||

*注:具体验收标准需根据产品规格书及客户协议调整执行参数。

【数据记录规范】 1.原始数据应包含: -设备校准证书编号 -环境温湿度记录(23±2℃/45±15%RH) -探针接触点显微图像 -完整的载荷-时间曲线 2.异常数据处理原则: -剔除探针滑移导致的无效数据 -同一批次允许5%数据离散度 -离散度>10%需启动过程追溯 3.报告输出要求: -中英文对照格式 -附失效模式分布图 -包含Weibull分布分析 -提供CPK过程能力指数

重要提示:执行晶圆级芯片测试时需特别注意: 1.采用非接触式定位技术避免表面损伤 2.控制静电放电风险(<100V HBM) 3.对于超薄芯片(厚度<50μm)应启用动态补偿算法 4.MEMS器件需在真空环境下完成测试

行业最新技术要求(2024版):

Chiplet架构下混合键合强度≥50MPa

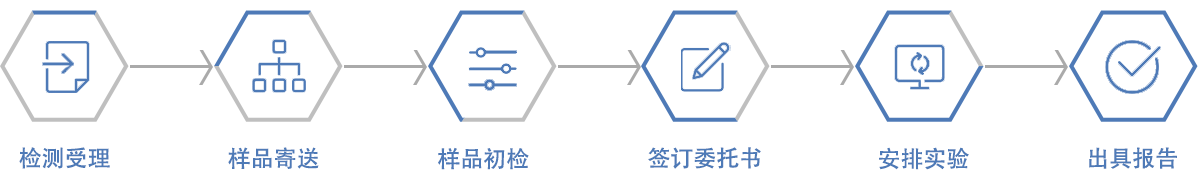

检测流程

线上咨询或者拨打咨询电话;

获取样品信息和检测项目;

支付检测费用并签署委托书;

开展实验,获取相关数据资料;

出具检测报告。

上一篇:试压块强度检测

下一篇:钢板弯曲强度检测